# CPE 323: The MSP430 Instruction Set Architecture

Aleksandar Milenkovic

Electrical and Computer Engineering The University of Alabama in Huntsville

milenka@ece.uah.edu

http://www.ece.uah.edu/~milenka

#### **Outline**

- Introduction

- Registers

- Memory

- **Addressing Modes**

- Instruction Set

- Instruction Formats and Encodings

Memory

Intro

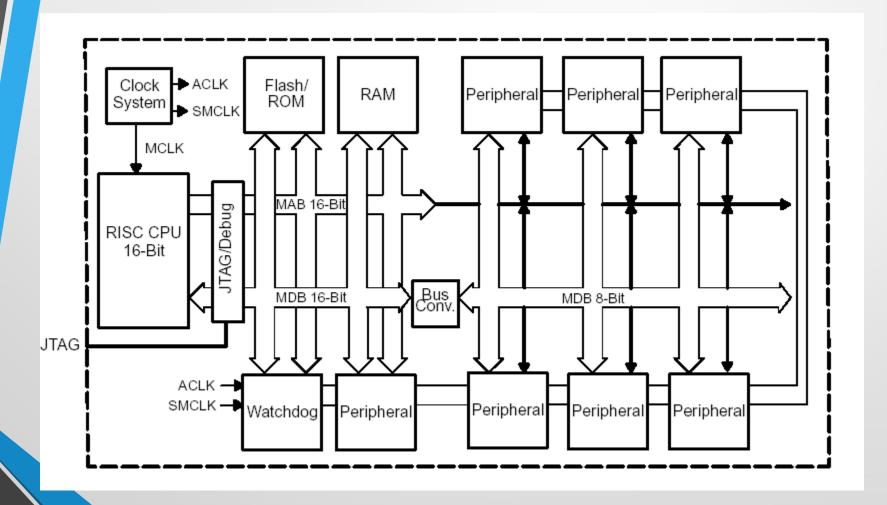

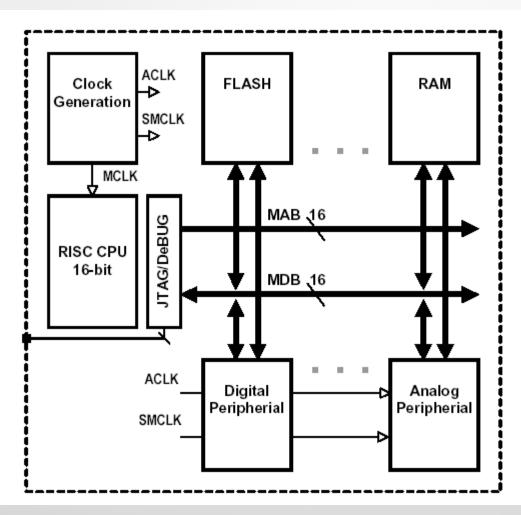

#### **MSP 430 Modular Architecture**

von-Neumann common bus connects CPU to all memory and peripherals

Embedded

emulation

accessed

in-application

with JTAG

Architecture reduces power consuming, noise generating fetches to memory

16-bit bus handles widewidth data much more effectively

Intro

#### MSP430 16-bit RISC

- Large 16-bit register file

- High-bandwidth 16-bit data and address bus

- RISC architecture with 27 instructions and 7 addressing modes

- Single-cycle register operations with full-access

- Direct memory-memory transfer designed for modern programming

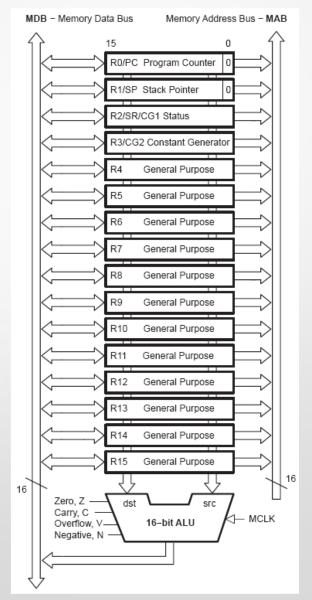

#### Registers

| 15 0<br>0                                                                               | RO - PC Program Counter<br>16-bit = no paging                                                              |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 15 0                                                                                    | R1 - SP Stack Pointer<br>Addressable = great "C" code                                                      |

| reserved for future enhancements V SCG1 SCG0 Osc Off Off Off Off Off Off Off Off Off Of | <b>R2 - SR Status Register</b><br>Define LPMx                                                              |

| 00000h 00001h 00002h 0004h 00008h 0FFFFh                                                | R3/R2 - CG Constant<br>Generator<br>automatic generation of<br>common used values reduces<br>code size 30% |

| 15 0                                                                                    | R4 - General Purpose                                                                                       |

| 15 0                                                                                    | R15 - General Purpose                                                                                      |

R4 through R15 are single-cycle, general purpose and identical in all respects - used for math, storage, and addressing modes.

#### PC/R0 – Program Counter

- The 16-bit program counter (PC/R0) points to the next instruction to be executed

- Each instruction uses an even number of bytes (two, four, or six), and the PC is incremented accordingly

- Instruction accesses in the 64-KB address space are performed on word boundaries, and the PC is aligned to even addresses

- PC can be addressed by all instructions and all addressing modes

- MOV #LABEL,PC; Branch to address LABEL

- MOV LABEL,PC; Branch to address contained in LABEL

- MOV @R14,PC; Branch indirect to address in R14

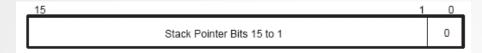

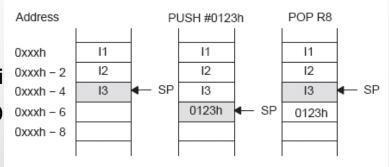

## SP/R1 – Stack Pointer

- The stack pointer (SP/R1) points to the current top of the stack

- It uses a predecrement, postincrement scheme (SP points to the top of the stack, and the stack grows toward lower addresses)

- SP can be used by software with all instructions and addressing modes

- Examples

- MOV 2 (SP), R6; Item I2 -> R6

- MOV R7,0(SP); Overwrite TOS wi

- PUSH #0123h; Put 0123h onto TO

- POP R8; R8 = 0123h

• Question: Illustrate the stack contents after PUSH SP and POP SP instructions are executed?

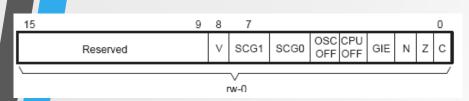

## SR/R2 – Status Register

Instruction Formats

The status register (SR/R2), used as a source or destination register, can be used in the register mode only addressed with word instructions

<u>Addressing</u>

The remaining combinations of addressing modes are used to support the constant generator

| Bit    | Description                                                                                                            | Description                                                                                 |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| V      | Overflow bit. This bit is set when overflows the signed-variable range                                                 | the result of an arithmetic operation le.                                                   |  |  |  |  |  |

|        | ADD(.B),ADDC(.B)                                                                                                       | Set when: Positive + Positive = Negative Negative + Negative = Positive, otherwise reset    |  |  |  |  |  |

|        | SUB(.B),SUBC(.B),CMP(.B)                                                                                               | Set when:  Positive – Negative = Negative  Negative – Positive = Positive,  otherwise reset |  |  |  |  |  |

| SCG1   | System clock generator 1. This bit                                                                                     | , when set, turns off the SMCLK.                                                            |  |  |  |  |  |

| SCG0   | System clock generator 0. This bit, when set, turns off the DCO dc generator, if DCOCLK is not used for MCLK or SMCLK. |                                                                                             |  |  |  |  |  |

| OSCOFF | Oscillator Off. This bit, when set, turns off the LFXT1 crystal oscillator, when LFXT1CLK is not use for MCLK or SMCLK |                                                                                             |  |  |  |  |  |

| CPUOFF | CPU off. This bit, when set, turns of                                                                                  | off the CPU.                                                                                |  |  |  |  |  |

| GIE    | General interrupt enable. This interrupts. When reset, all maskab                                                      | bit, when set, enables maskable<br>le interrupts are disabled.                              |  |  |  |  |  |

| N      | Negative bit. This bit is set when the is negative and cleared when the i                                              | ne result of a byte or word operation result is not negative.                               |  |  |  |  |  |

|        | Word operation:                                                                                                        | N is set to the value of bit 15 of the result                                               |  |  |  |  |  |

|        | Byte operation:                                                                                                        | N is set to the value of bit 7 of the result                                                |  |  |  |  |  |

| Z      | Zero bit. This bit is set when the re and cleared when the result is not                                               | esult of a byte or word operation is 0<br>0.                                                |  |  |  |  |  |

| С      | Carry bit. This bit is set when the produced a carry and cleared whe                                                   | e result of a byte or word operation<br>n no carry occurred.                                |  |  |  |  |  |

#### **Constant Generation**

- Six commonly-used constants are generated with the constant generator registers R2 and R3

- Adv.: No special instructions, no special code, no extra memory access

- Assembler uses the constant generator automatically if one of the six constants is used as an immediate source operand.

Registers R2 and R3, used in the constant mode, cannot be addressed explicitly; they act as source-only registers.

- The constants are selected with the source-register addressing modes (As), as described below.

| Register | As | Constant | Remarks                               |

|----------|----|----------|---------------------------------------|

| R2       | 00 |          | Register mode                         |

| R2       | 01 | (0)      | Absolute address mode                 |

| R2       | 10 | 00004h   | +4, bit processing                    |

| R2       | 11 | 00004H   |                                       |

|          |    |          | +8, bit processing                    |

| R3       | 00 | 00000h   | 0, word processing                    |

| R3       | 01 | 00001h   | +1                                    |

| R3       | 10 | 00002h   | +2, bit processing                    |

| R3       | 11 | 0FFFFh   | <ul><li>–1, word processing</li></ul> |

#### **Constant Generation**

- Constant generator allows for additional 24 instructions that are emulated

- Examples

- CLR dst MOV R3,dst

- INC dst ADD 0(R3),dst

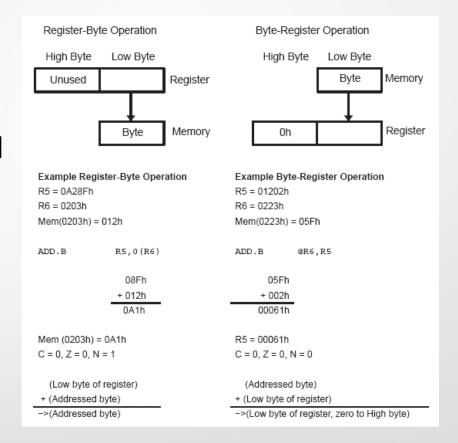

Memory

#### **General-Purpose Registers**

• The twelve registers, R4–R15, are general-purpose registers. All of these registers can be used as data registers, address pointers, or index values and can be accessed with byte or word instructions as shown below

#### **Memory Organization**

- Word alignment

- Bytes are located at even or odd addresses

- Words are only located at even addresses

- Endianess (little-endian)

- When using word instructions, only even addresses may be used

- The Low byte of a word is always an even address

- The high byte is at the next odd address

- For example, if a data word is located at address xxx4h, then the low byte of that data word is located at address xxx4h, and the high byte of that word is located at address xxx5h

|    |       | •••          |     |   | xxxAh |

|----|-------|--------------|-----|---|-------|

| 15 | 14    | Bits         | 9   | 8 | xxx9h |

| 7  | 6     | Bits         | 1   | 0 | xxx8h |

|    |       | Byte         |     |   | xxx7h |

|    |       | Byte         |     |   | xxx6h |

|    | W     | ord (High By | te) |   | xxx5h |

|    | W     | ord (Low By  | te) |   | xxx4h |

|    | xxx3h |              |     |   |       |

Intro

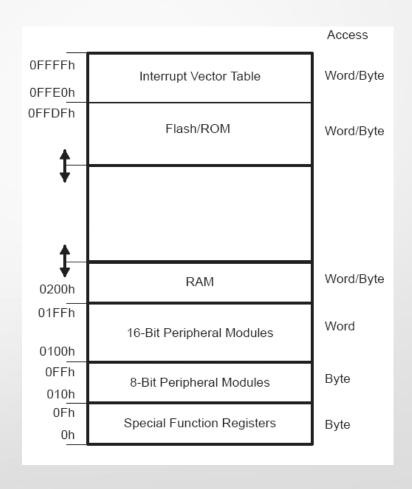

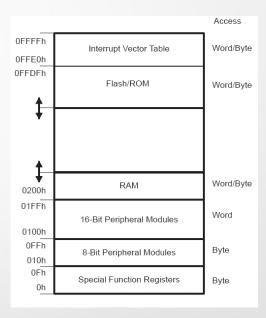

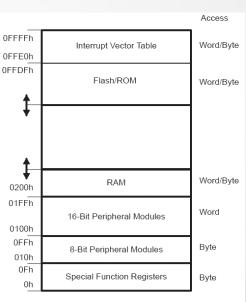

#### **Address Space**

- von-Neumann architecture: one address space shared with special function registers (SFRs), peripherals, RAM, and Flash/ROM memory as shown

- Memory maps are device specific

- Code access are always performed on even addresses

- Data can be accessed as bytes or words

- The addressable memory space is 64 KB

- Extended architecture allows for 1 MB address space

#### Address Space (cont'd)

- Special Function Registers (SFRs)

- Some peripheral functions are configured in the SFRs

- The SFRs are located in the lower 16 bytes of the address space, and are organized by byte

- SFRs must be accessed using byte instructions only

- Peripheral modules (PM)

- Peripheral modules are mapped into the address space

- Address space 0100-01FFh is reserved for 16-bit PMs

- Should be accessed with word instructions

- If byte instructions are used, only even addresses are permissible, and the high byte of the result is always 0

- Address space 010h-0FFh is reserved for 8-bit PMs

- Should be accessed with byte instructions

- Read access of byte modules using word instructions results in unpredictable data in the high byte

- If word data is written to a byte module only the low byte is written into the peripheral register, ignoring the high byte

#### Address Space (cont'd)

- RAM

- RAM starts at 0200h

- End address of RAM depends on the amount of RAM present and varies by device

- RAM can be used for both code and data

- Flash/ROM

- Start address of Flash/ROM depends on the amount of Flash/ROM present and varies by device

- End address for Flash/ROM is 0FFFFh

- Flash can be used for both code and data;

Word or byte tables can be stored and used in Flash/ROM without the need to copy the tables to RAM before using them

- Interrupt vector table

- Is mapped into the upper 16/32 words of Flash/ROM address space, with the highest priority interrupt vector at the highest Flash/ROM word address (OFFFEh)

#### **Addressing Modes**

- Register (a.k.a., register direct)

- Indexed

- Symbolic (a.k.a., PC relative, special case of indexed)

- Absolute (special case of indexed)

- Register indirect

- Register indirect with autoincrement

- Immediate

#### **Addressing Modes**

Seven addressing modes for the source operand and four addressing modes for the destination operand can address the complete address space with no exceptions.

Table 2. Address Mode Descriptions

| ADDRESS MODE           | s                    | D | SYNTAX          | EXAMPLE                     | OPERATION         |

|------------------------|----------------------|---|-----------------|-----------------------------|-------------------|

| Register               | ● ● MOV Rs,Rd        |   | MOV Rs,Rd       | MOV R10,R11                 | R10> R11          |

| Indexed                | •                    | • | MOV X(Rn),Y(Rm) | MOV 2(R5),6(R6)             | M(2+R5)> M(6+R6)  |

| Symbolic (PC relative) | •                    | • | MOV EDE, TONI   |                             | M(EDE)> M(TONI)   |

| Absolute               | te ● MOV &MEM,&TCDAT |   | MOV &MEM,&TCDAT |                             | M(MEM)> M(TCDAT)  |

| Indirect               | •                    |   | MOV @Rn,Y(Rm)   | MOV @R10,Tab(R6)            | M(R10)> M(Tab+R6) |

| Indirect autoincrement | MOV @Rn+ Rm          |   | MOV @R10+,R11   | M(R10)> R11<br>R10 + 2> R10 |                   |

| Immediate              | •                    |   | MOV #X,TONI     | MOV #45,TONI                | #45> M(TONI)      |

NOTE: S = source D = destination

#### **Addressing Modes**

**Instruction Formats**

The bit numbers in the table below describe the contents of the As (source) and Ad (destination) mode bits

| As/Ad | Addressing Mode           | Syntax | Description                                                                                                                 |

|-------|---------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| 00/0  | Register mode             | Rn     | Register contents are operand                                                                                               |

| 01/1  | Indexed mode              | X(Rn)  | (Rn + X) points to the operand. X is stored in the next word.                                                               |

| 01/1  | Symbolic mode             | ADDR   | (PC + X) points to the operand. X is stored in the next word. Indexed mode X(PC) is used.                                   |

| 01/1  | Absolute mode             | &ADDR  | The word following the instruction contains the absolute address. X is stored in the next word. Indexed mode X(SR) is used. |

| 10/-  | Indirect register mode    | @Rn    | Rn is used as a pointer to the operand.                                                                                     |

| 11/-  | Indirect<br>autoincrement | @Rn+   | Rn is used as a pointer to the operand. Rn is incremented afterwards by 1 for .B instructions and by 2 for .W instructions. |

| 11/-  | Immediate mode            | #N     | The word following the instruction contains the immediate constant N. Indirect autoincrement mode @PC+ is used.             |

#### **Register Addressing Mode**

| Op-Code | Source-Regist | er Ad | B/W | As | Destination-Register |

|---------|---------------|-------|-----|----|----------------------|

| 0100    | 0100          | 0     | 0   | 00 | 0101                 |

|         |               |       |     |    |                      |

| 4405    | mov.w         | R4,R5 |     |    | ;                    |

| 4445    | mov.b         | R4,R5 |     |    | ;                    |

Valid for Source and destination As=00, Ad=0

The operand is contained in one of the CPU registers R0 to R15. This is the fastest addressing mode and needs the least memory .

## Register Addressing Mode (cont'd)

Example: MOV R10,R11 Before: After: 0A023h R10 0A023h R10 0FA15h R11 R11 0A023h  $PC_{old}$ PC  $PC_{old} + 2$ PC

#### Note: Data in Registers

The data in the register can be accessed using word or byte instructions. If byte instructions are used, the high byte is always 0 in the result. The status bits are handled according to the result of the byte instruction.

## Register-Indexed Addressing Mode

|   | Op-Code              | Source-Register | r Ad  | B/W  | As      | Destination-Register |

|---|----------------------|-----------------|-------|------|---------|----------------------|

| • | 0100                 | 0100            | 1     | 0    | 01      | 0101                 |

|   |                      |                 |       |      |         |                      |

|   | <b>4495</b> 01000200 | mov.w 1         | 00h(R | 24), | 200h (R | 5) ;                 |

44150100 mov.w 100h(R4),R5 ;

Valid for Source and destination As=01, Ad=1

The address of the operand is the sum of the index and the contents of the register.

# Register-Indexed Addressing Mode (cont'd)

| Example: MOV 2(R5),6(R6);  |                            |                              |                            |                                      |                        |  |  |  |

|----------------------------|----------------------------|------------------------------|----------------------------|--------------------------------------|------------------------|--|--|--|

| Before:                    | Address<br>Space           | Register                     | After:                     | Address<br>Space                     | Register               |  |  |  |

| 0FF16h<br>0FF14h<br>0FF12h | 00006h<br>00002h<br>04596h | R5 01080h<br>R6 0108Ch<br>PC | 0FF16h<br>0FF14h<br>0FF12h | 0xxxxh<br>00006h<br>00002h<br>04596h | R5 01080h<br>R6 0108Ch |  |  |  |

| 01094h<br>01092h<br>01090h | Oxxxxh<br>O5555h<br>Oxxxxh | 0108Ch<br>+0006h<br>01092h   | 01094h<br>01092h<br>01090h | 0xxxxh<br>01234h<br>0xxxxh           |                        |  |  |  |

| 01084h<br>01082h<br>01080h | 0xxxxh<br>01234h<br>0xxxxh | 01080h<br>+0002h<br>01082h   | 01084h<br>01082h<br>01080h | Oxxxxh<br>O1234h<br>Oxxxxh           |                        |  |  |  |

## **Symbolic Addressing Mode**

Instruction Formats

| Op-Code                            | Source-Register |      | Ad | B/W | As | Destination-Register |

|------------------------------------|-----------------|------|----|-----|----|----------------------|

| 0100                               | 0000            |      | 1  | 0   | 01 | 0000                 |

|                                    |                 |      |    |     |    |                      |

| <b>4<u>0</u>9<u>0</u></b> ffa80006 | mov.w           | EDE, | ТО | NI  |    | ;                    |

| 4015ffac                           | mov.w           | EDE, | R5 |     |    | ;                    |

#### Source and destination As=01, Ad=1

Addressing

The content of the addresses EDE / TONI are used for the operation. The source or destination address is computed as a difference from the PC and uses the PC in indexed addressing mode. Any address in the 64k memory space is addressable.

# Symbolic Addressing Mode (cont'd)

| Example:                   | MOV EDE, TONI ; Source address EDE = 0F016h ; Dest. address TONI=01114h |                     |     |                            |                            |                  |  |  |

|----------------------------|-------------------------------------------------------------------------|---------------------|-----|----------------------------|----------------------------|------------------|--|--|

| Before:                    | Address<br>Space                                                        | Registe             |     | After:                     | Address<br>Space           | Register<br>I PC |  |  |

| 0FF16h                     | 011FEh                                                                  |                     |     | 0FF16h                     | 011FEh                     |                  |  |  |

| 0FF14h                     | 0F102h                                                                  |                     |     | 0FF14h                     | 0F102h                     |                  |  |  |

| 0FF12h                     | 04090h                                                                  | PC                  |     | 0FF12h                     | 04090h                     |                  |  |  |

| 0F018h<br>0F016h<br>0F014h | 0xxxxh<br>0A123h<br>0xxxxh                                              | 0FF<br>+0F10<br>0F0 | 02h | 0F018h<br>0F016h<br>0F014h | 0xxxxh<br>0A123h<br>0xxxxh |                  |  |  |

| 01116h<br>01114h<br>01112h | 0xxxxh<br>05555h<br>0xxxxh                                              | 0FF<br>+011F<br>011 | Eh_ | 01116h<br>01114h<br>01112h | 0xxxxh<br>0A123h<br>0xxxxh |                  |  |  |

#### **Absolute Addressing Mode**

Instruction Formats

| Op-Code                        | Source-Regis | ster | Ad  | B/W | As | Destination-Register |

|--------------------------------|--------------|------|-----|-----|----|----------------------|

| 0100                           | 0010         |      | 1   | 0   | 01 | 0010                 |

|                                |              |      |     |     |    |                      |

| 4 <u>2</u> 9 <u>2</u> 01720174 | mov.w        | &CC  | RO, | &CC | R1 | ;                    |

| 42150172                       | mov.w        | &CC  | RO, | R5  |    | ;                    |

#### Source and destination As=01, Ad=1

The contents of the fixed addresses are used for the operation. The SR is used in the indexed mode to create an absolute 0. Use for hardware peripherals located at an absolute address that can never be relocated.

# Absolute Addressing Mode (cont'd)

| Example: | MOV              | &EDE,&TONI | ;Source ad; |                  |          |

|----------|------------------|------------|-------------|------------------|----------|

| Before:  | Address<br>Space | Register   | After:      | Address<br>Space | Register |

| 0FF16h   | 01114h           |            | 0FF16h      | 0xxxxh<br>01114h | PC       |

| 0FF14h   | 0F016h           |            | 0FF14h      | 0F016h           |          |

| 0FF12h   | 04292h           | PC         | 0FF12h      | 04292h           |          |

|          |                  |            |             |                  |          |

|          |                  |            |             | $\square$        |          |

| 0F018h   | 0xxxxh           |            | 0F018h      | 0xxxxh           |          |

| 0F016h   | 0A123h           |            | 0F016h      | 0A123h           |          |

| 0F014h   | 0xxxxh           |            | 0F014h      | 0xxxxh           |          |

|          |                  |            |             |                  |          |

|          |                  |            |             |                  | 1        |

| 01116h   | 0xxxxh           |            | 01116h      | 0xxxxh           |          |

| 01114h   | 01234h           |            | 01114h      | 0A123h           |          |

| 01112h   | 0xxxxh           |            | 01112h      | 0xxxxh           |          |

|          |                  |            |             |                  |          |

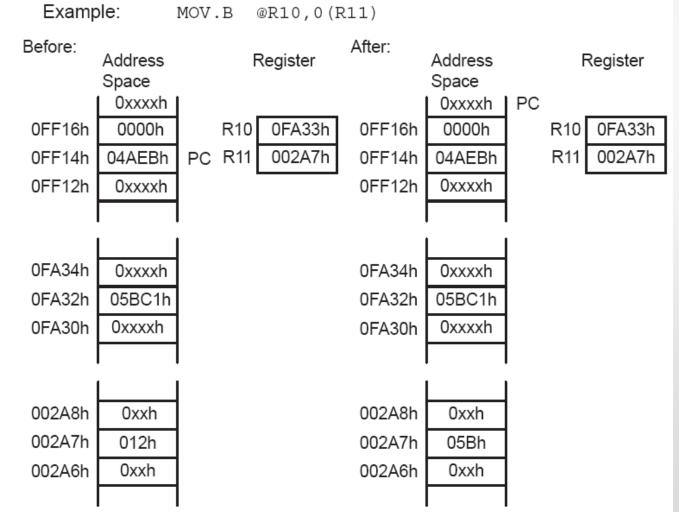

#### Register Indirect Addressing Mode

**Instruction Formats**

| Op-Code | Source-Register | Ad   | B/W | As | Destination-Register |

|---------|-----------------|------|-----|----|----------------------|

| 0100    | 0100            | 0    | 0   | 10 | 0101                 |

|         |                 |      |     |    |                      |

| 4425    | mov.w @R        | 4,R5 |     |    | ;                    |

| 4465    | mov.b @R        | 4,R5 |     |    | ;                    |

#### Source only As=10, Ad=n/a

The registers are used as a pointer to the operand.

The indexed mode with zero index may be used for "indirect register addressing" of the destination operand.

44a50000

mov.w

@R4,0(R5)

## Register Indirect Addressing Mode (cont'd)

## Register Indirect Autoincrement AM

**Instruction Formats**

| Op-Code | Source-Register | Ad   | B/W | As | Destination-Register |

|---------|-----------------|------|-----|----|----------------------|

| 0100    | 0100            | 0    | 0   | 11 | 0101                 |

|         |                 |      |     |    |                      |

| 4435    | mov.w @F        | 4+,R | 5   |    | ;                    |

| 4475    | mov.b @R        | 4+,R | 5   |    | ;                    |

#### Source only As=11, Ad=n/a

The registers are used as a pointer to the operand. The registers are incremented afterwards - by 1 in byte mode, by 2 in word mode.

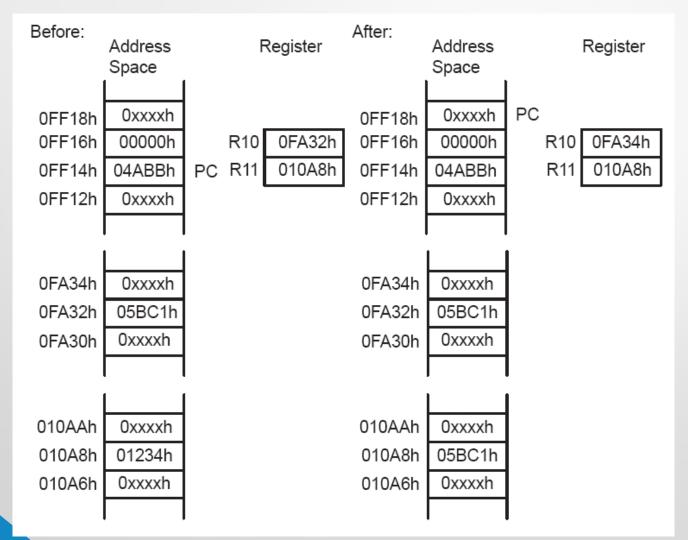

## Register Indirect Autoincrement AM (cont'd)

Memory

#### **Immediate Addressing Mode**

|   | Op-Code | Source-Register | Ad | B/W | As | Destination-Register |

|---|---------|-----------------|----|-----|----|----------------------|

| • | 0100    | 0000            | 0  | 0   | 11 | 0101                 |

**4<u>0</u>35**1234

mov.w

#1234h,R5

; Any 16-bit value

#### Source only As=11, Ad=n/a

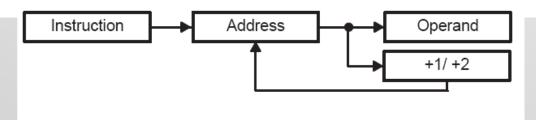

Any immediate 8 or 16 bit constant can be used with the instruction. The PC is used in autoincrement mode to emulate this addressing mode.

# Immediate Addressing Mode (cont'd)

| Example: | VOM              | #45h,TONI |        |                  |    |          |

|----------|------------------|-----------|--------|------------------|----|----------|

| Before:  | Address<br>Space | Register  | After: | Address<br>Space |    | Register |

|          |                  |           | 0FF18h | 0xxxxh           | PC |          |

| 0FF16h   | 01192h           |           | 0FF16h | 01192h           |    |          |

| 0FF14h   | 00045h           |           | 0FF14h | 00045h           |    |          |

| 0FF12h   | 040B0h           | PC        | 0FF12h | 040B0h           |    |          |

|          |                  |           |        |                  |    |          |

|          |                  | 0FF16h    |        |                  | 1  |          |

| 010AAh   | 0xxxxh           | +01192h   | 010AAh | 0xxxxh           |    |          |

| 010A8h   | 01234h           | 010A8h    | 010A8h | 00045h           |    |          |

| 010A6h   | 0xxxxh           |           | 010A6h | 0xxxxh           |    |          |

|          |                  |           |        |                  |    |          |

|          |                  |           |        |                  |    |          |

#### **Instruction Set**

- 27 core instructions

- Have unique op-codes decoded by the CPU

- 24 emulated instructions

- Make code easier to write and read, but do not have op-codes; instead an equivalent core instruction is generated

- No code or performance penalty for using emulated instructions

- 3 core instruction formats

- **Dual-operand**

- Single-operand

- Jump

- All single- and dual-operand instructions can be byte or word instructions by using .B or .W (default) extensions

- Byte instructions are used to access byte data or byte peripherals

- Word instructions are used to access word data or word peripherals

#### **27 Core RISC Instructions**

| Format I            | Format II      | Format III      |

|---------------------|----------------|-----------------|

| Source, Destination | Single Operand | +/- 9bit Offset |

| add(.b)             | call           | jmp             |

| addc(.b)            | swpb           | jc              |

| and(.b)             | sxt            | jnc             |

| bic(.b)             | push(.b)       | jeq             |

| bis(.b)             | reti           | jne             |

| bit(.b)             | rra(.b)        | jge             |

| cmp(.b)             | rrc(.b)        | jl              |

| dadd(.b)            |                | jn              |

| mov(.b)             |                |                 |

| sub(.b)             |                |                 |

| subc(.b)            |                |                 |

| xor(.b)             |                |                 |

#### **Emulated Instructions: Examples**

```

// clear carry

clrc

; Clear Carry bit

bic.w \#0x01, SR ; Clear Bit 0 in SR

// decrement

dec.w R14

; Decrement R14

sub.w \#0x01, R4 ; Core instruction

// return from subroutine

ret

mov.w @SP+, PC

```

#### **51 Total Instructions**

| Format I            | Format II      | Format III      | Support |

|---------------------|----------------|-----------------|---------|

| Source, Destination | Single Operand | +/- 9bit Offset |         |

| add(.b)             | br             | jmp             | clrc    |

| addc(.b)            | call           | jc              | setc    |

| and(.b)             | swpb           | jnc             | clrz    |

| bic(.b)             | sxt            | jeq             | setz    |

| bis(.b)             | push(.b)       | jne             | clrn    |

| bit(.b)             | pop.(b)        | jge             | setn    |

| cmp(.b)             | rra(.b)        | jl              | dint    |

| dadd(.b)            | rrc(.b)        | jn              | eint    |

| mov(.b)             | inv(.b)        |                 | nop     |

| sub(.b)             | inc(.b)        |                 | ret     |

| subc(.b)            | incd(.b)       |                 | reti    |

| xor(.b)             | dec(.b)        |                 |         |

|                     | decd(.b)       |                 |         |

|                     | adc(b)         |                 |         |

|                     | sbc(.b)        |                 |         |

|                     | clr(.b)        |                 |         |

|                     | dadc(.b)       |                 |         |

|                     | rla(.b)        |                 |         |

|                     | rlc(.b)        |                 |         |

|                     | tst(.b)        |                 |         |

gisters Memory Addressing Instruction Set Instruction Format

## **Double operand instructions**

| 15 14 13 | 12 | 11 | 10  | 9  | 8 | 7  | 6   | 5 | 4  | 3 | 2   | 1  | 0 |

|----------|----|----|-----|----|---|----|-----|---|----|---|-----|----|---|

| Op-code  |    |    | S-R | eg |   | Ad | B/W |   | As |   | D-R | eg |   |

| Mnemonic | S-Reg,  | Operation                                                 |   | State | us Bit | s |

|----------|---------|-----------------------------------------------------------|---|-------|--------|---|

|          | D-Reg   |                                                           | ٧ | N     | Z      | С |

| MOV(.B)  | src,dst | $src \to dst$                                             | _ | _     | _      | _ |

| ADD(.B)  | src,dst | $\text{src} + \text{dst} \rightarrow \text{dst}$          | * | *     | *      | * |

| ADDC(.B) | src,dst | $src + dst + C \rightarrow dst$                           | * | *     | *      | * |

| SUB(.B)  | src,dst | $dst + .not.src + 1 \rightarrow dst$                      | * | *     | *      | * |

| SUBC(.B) | src,dst | $\text{dst + .not.src + C} \rightarrow \text{dst}$        | * | *     | *      | * |

| CMP(.B)  | src,dst | dst – src                                                 | * | *     | *      | * |

| DADD(.B) | src,dst | $\text{src + dst + C} \rightarrow \text{dst (decimally)}$ | * | *     | *      | * |

| BIT(.B)  | src,dst | src .and. dst                                             | 0 | *     | *      | * |

| BIC(.B)  | src,dst | .not.src .and. dst $\rightarrow$ dst                      | _ | _     | _      | _ |

| BIS(.B)  | src,dst | $\text{src .or. dst} \rightarrow \text{dst}$              | _ | _     | _      | _ |

| XOR(.B)  | src,dst | $\text{src .xor. dst} \to \text{dst}$                     | * | *     | *      | * |

| AND(.B)  | src,dst | src .and. dst $ ightarrow$ dst                            | 0 | *     | *      | * |

## **Single Operand Instruction**

| 15 | 14 | 13 | 12 | 11     | 10 | 9 | 8 | 7 | 6   | 5 | 4  | 3 | 2    | 1   | 0 |

|----|----|----|----|--------|----|---|---|---|-----|---|----|---|------|-----|---|

|    |    |    | 0  | p-code | Э  |   |   |   | B/W |   | Ad |   | D/S- | Reg |   |

| Mnemonic | S-Reg, | Operation                                          | Stat | us Bi | ts |   |

|----------|--------|----------------------------------------------------|------|-------|----|---|

|          | D-Reg  |                                                    | V    | N     | Z  | С |

| RRC(.B)  | dst    | $C \to MSB \to \dots \dots LSB \to C$              | *    | *     | *  | * |

| RRA(.B)  | dst    | $MSB \to MSB \to LSB \to C$                        | 0    | *     | *  | * |

| PUSH(.B) | src    | $SP-2 \rightarrow SP,src \rightarrow @SP$          | -    | _     | _  | _ |

| SWPB     | dst    | Swap bytes                                         | -    | _     | _  | _ |

| CALL     | dst    | $SP-2 \rightarrow SP, PC\text{+}2 \rightarrow @SP$ | -    | _     | _  | _ |

|          |        | $\text{dst} \to \text{PC}$                         |      |       |    |   |

| RETI     |        | $TOS \rightarrow SR,SP + 2 \rightarrow SP$         | *    | *     | *  | * |

|          |        | $TOS \rightarrow PC, SP + 2 \rightarrow SP$        |      |       |    |   |

| SXT      | dst    | Bit $7 \rightarrow$ Bit 8Bit 15                    | 0    | *     | *  | * |

## **Jump Instructions**

| 15 | 14     | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5     | 4      | 3      | 2 | 1 | 0 |

|----|--------|----|----|----|----|---|---|---|---|-------|--------|--------|---|---|---|

|    | Ор-сос | le |    | С  |    |   |   |   |   | 10-Bi | t PC C | Offset |   |   |   |

| Mnemonic | S-Reg, D-Reg | Operation                            |

|----------|--------------|--------------------------------------|

| JEQ/JZ   | Label        | Jump to label if zero bit is set     |

| JNE/JNZ  | Label        | Jump to label if zero bit is reset   |

| JC       | Label        | Jump to label if carry bit is set    |

| JNC      | Label        | Jump to label if carry bit is reset  |

| JN       | Label        | Jump to label if negative bit is set |

| JGE      | Label        | Jump to label if (N .XOR. V) = 0     |

| JL       | Label        | Jump to label if (N .XOR. V) = 1     |

| JMP      | Label        | Jump to label unconditionally        |

#### **3 Instruction Formats**

| ; | Format | Ι | Source | and | Destination |

|---|--------|---|--------|-----|-------------|

|---|--------|---|--------|-----|-------------|

|         | Op-Code | Source-Register |      | Source-Register Ad B/W As |  | As | Desti | nation-Register |       |

|---------|---------|-----------------|------|---------------------------|--|----|-------|-----------------|-------|

| 5       | 405     | add.w           | R4,F | 15                        |  |    | ;     | R4+R5=R5        | XXXX  |

| <u></u> | 3445    | add.b           | R4,R | 25                        |  |    | ;     | R4+R5=R5        | 0.0xx |

#### ; Format II Destination Only

|      | Op-Code | B/W | Ad | D/S- Register |   |

|------|---------|-----|----|---------------|---|

| 6404 | rlc.w   | R4  |    |               | ; |

| 6444 | rlc.b   | R4  |    |               | ; |

#### Format III There are 8(Un)conditional Jumps

|   | Op-Code | Condition | 10-bit PC offs | set |            |

|---|---------|-----------|----------------|-----|------------|

| 3 | 3c28    | jmp       | Loop_1         | ;   | Goto Loop_ |

$$PC_{new} = PC_{old} + 2 + PC_{offset} \times 2$$

## **Instruction Cycles and Lengths**

**Instruction Formats**

- The number of CPU clock cycles required for an instruction depends on the instruction format and the addressing modes used - not the instruction itself

- The number of clock cycles refers to the MCLK

Registers Memory Addressing Instruction Set Instruction Formats

# THE UNIVERSITY OF ALABAMA IN HUNTSVILLE

# Format I: Instruction Cycles and Length

Table 3–16. Format 1 Instruction Cycles and Lengths

| Addres | sing Mode | No. of | Length of   |     |              |

|--------|-----------|--------|-------------|-----|--------------|

| Src    | Dst       | Cycles | Instruction |     | Example      |

| Rn     | Rm        | 1      | 1           | MOV | R5,R8        |

|        | PC        | 2      | 1           | BR  | R9           |

|        | x(Rm)     | 4      | 2           | ADD | R5,4(R6)     |

|        | EDE       | 4      | 2           | XOR | R8,EDE       |

|        | &EDE      | 4      | 2           | MOV | R5, &EDE     |

| @Rn    | Rm        | 2      | 1           | AND | @R4,R5       |

|        | PC        | 2      | 1           | BR  | @R8          |

|        | x(Rm)     | 5      | 2           | XOR | @R5,8(R6)    |

|        | EDE       | 5      | 2           | MOV | @R5,EDE      |

|        | &EDE      | 5      | 2           | XOR | @R5,&EDE     |

| @Rn+   | Rm        | 2      | 1           | ADD | @R5+,R6      |

|        | PC        | 3      | 1           | BR  | @R9+         |

|        | x(Rm)     | 5      | 2           | XOR | @R5,8(R6)    |

|        | EDE       | 5      | 2           | MOV | @R9+,EDE     |

|        | &EDE      | 5      | 2           | MOV | @R9+,&EDE    |

| #N     | Rm        | 2      | 2           | MOV | #20,R9       |

|        | PC        | 3      | 2           | BR  | #2AEh        |

|        | x(Rm)     | 5      | 3           | MOV | #0300h,0(SP) |

|        | EDE       | 5      | 3           | ADD | #33,EDE      |

|        | &EDE      | 5      | 3           | ADD | #33,&EDE     |

| x(Rn)  | Rm        | 3      | 2           | MOV | 2(R5),R7     |

|        | PC        | 3      | 2           | BR  | 2 (R6)       |

|        | TONI      | 6      | 3           | MOV | 4(R7),TONI   |

|        | x(Rm)     | 6      | 3           | ADD | 4(R4),6(R9)  |

|        | &TONI     | 6      | 3           | MOV | 2(R4),&TONI  |

| EDE    | Rm        | 3      | 2           | AND | EDE,R6       |

|        | PC        | 3      | 2           | BR  | EDE          |

|        | TONI      | 6      | 3           | CMP | EDE, TONI    |

|        | x(Rm)     | 6      | 3           | MOV | EDE,0(SP)    |

|        | &TONI     | 6      | 3           | MOV | EDE, &TONI   |

| &EDE   | Rm        | 3      | 2           | MOV | &EDE,R8      |

|        | PC        | 3      | 2           | BRA | &EDE         |

|        | TONI      | 6      | 3           | MOV | &EDE, TONI   |

|        | x(Rm)     | 6      | 3           | MOV | &EDE,0(SP)   |

|        | &TONI     | 6      | 3           | MOV | &EDE, &TONI  |

## Format II and Format III: Instruction Cycles and Length

Table 3-15. Format-II Instruction Cycles and Lengths

|                    | No.                   | of Cycles |      | _                        |              |

|--------------------|-----------------------|-----------|------|--------------------------|--------------|

| Addressing<br>Mode | RRA, RRC<br>SWPB, SXT | PUSH      | CALL | Length of<br>Instruction | Example      |

| Rn                 | 1                     | 3         | 4    | 1                        | SWPB R5      |

| @Rn                | 3                     | 4         | 4    | 1                        | RRC @R9      |

| @Rn+               | 3                     | 5         | 5    | 1                        | SWPB @R10+   |

| #N                 | (See note)            | 4         | 5    | 2                        | CALL #0F000h |

| X(Rn)              | 4                     | 5         | 5    | 2                        | CALL 2(R7)   |

| EDE                | 4                     | 5         | 5    | 2                        | PUSH EDE     |

| &EDE               | 4                     | 5         | 5    | 2                        | SXT &EDE     |

- Format III: all jump instructions take 2 clock cycles to execute and are 1 word long

- Interrupt and reset cycles

Table 3-14. Interrupt and Reset Cycles

| Action                       | No. of<br>Cycles | Length of<br>Instruction |

|------------------------------|------------------|--------------------------|

| Return from interrupt (RETI) | 5                | 1                        |

| Interrupt accepted           | 6                | -                        |

| WDT reset                    | 4                | -                        |

| Reset (RST/NMI)              | 4                | -                        |

## **Instruction Encoding**

|      | 000     | 040   | 080  | 0C0 | 100 | 140   | 180 | 1C0      | 200   | 240    | 280  | 2C0 | 300  | 340 | 380 | 3C0 |

|------|---------|-------|------|-----|-----|-------|-----|----------|-------|--------|------|-----|------|-----|-----|-----|

| 0xxx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 4xxx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 8xxx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| Cxxx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 1xxx | RRC     | RRC.B | SWPB |     | RRA | RRA.B | SXT |          | PUSH  | PUSH.B | CALL |     | RETI |     |     |     |

| 14xx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 18xx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 1Cxx |         |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 20xx | JNE/JNZ |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 24xx | JEQ/JZ  |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 28xx | JNC     |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 2Cxx | JC      |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 30xx | JN      |       |      |     |     |       |     |          |       |        |      |     |      |     |     |     |

| 34xx |         |       |      |     |     |       | J   | IGE      |       |        |      |     |      |     |     |     |

| 38xx |         |       |      |     |     |       |     | IL       |       |        |      |     |      |     |     |     |

| 3Схх |         |       |      |     |     |       | J   | MP       |       |        |      |     |      |     |     |     |

| 4xxx |         |       |      |     |     |       | Ν   | ИOV, N   | IOV.B |        |      |     |      |     |     |     |

| 5xxx |         |       |      |     |     |       |     | ADD, A   |       |        |      |     |      |     |     |     |

| 6xxx |         |       |      |     |     |       | A   | ADDC,    | ADDC. | В      |      |     |      |     |     |     |

| 7xxx |         |       |      |     |     |       | 5   | SUBC,    | SUBC. | В      |      |     |      |     |     |     |

| 8xxx |         |       |      |     |     |       | 9   | SUB, S   | UB.B  |        |      |     |      |     |     |     |

| 9ххх |         |       |      |     |     |       | (   | CMP, C   | MP.B  |        |      |     |      |     |     |     |

| Axxx |         |       |      |     |     |       |     | DADD,    | DADD. | В      |      |     |      |     |     |     |

| Bxxx |         |       |      |     |     |       | Е   | BIT, BIT | .В    |        |      |     |      |     |     |     |

| Cxxx |         |       |      |     |     |       | Е   | BIC, BIG | C.B   |        |      |     |      |     |     |     |

| Dxxx |         |       |      |     |     |       | Е   | BIS, BIS | S.B   |        |      |     |      |     |     |     |

| Exxx |         |       |      |     |     |       |     | (OR, X   |       |        |      |     |      |     |     |     |

| Fxxx |         |       |      |     |     |       | 1   | AND, A   | ND B  |        |      |     |      |     |     |     |

#### **MSP 430 System Architecture: A Closer Look**