# CPE 323: MSP430 LCD\_A Controller

Aleksandar Milenkovic

Electrical and Computer Engineering The University of Alabama in Huntsville

milenka@ece.uah.edu

http://www.ece.uah.edu/~milenka

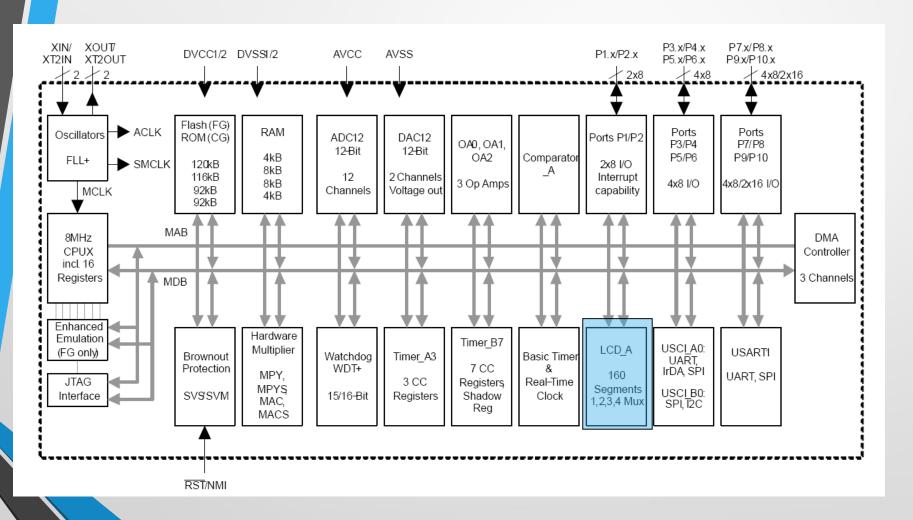

#### MSP430xG461x Microcontroller

#### **LCD Displays**

- LCD Liquid crystal display

- Use much less power than LEDs

- Does not emit light itself but controls the intensity of reflected or transmitted light

- Backlight must be provided for a display to be used in dark surroundings

- Three classes

- Segmented LCDs

- Character-based LCDs

- Fully graphical LCDs

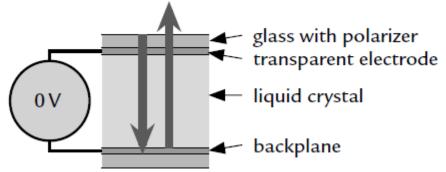

## **Reflective LCD: Operation Basics**

- Construction: two glass plates carry transparent electrodes on their opposing faces and there is a mirror below the lower plate

- Gap between is filled with a liquid crystal

- Bias voltage between electrodes = 0 =>

Incident light is reflected and the display appears clear

- Sufficiently large bias voltage changes the optical properties of the liquid crystal so that reflected light is no longer transmitted through the upper glass and the segment appears dark

- Electrically the display is similar to a capacitor, albeit rather lossy

(a) No voltage applied: incident light reflected (b) Voltage applied: light absorbed

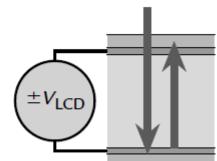

## Reflective LCD: Operation Basics (cont'd)

- Complication: LCDs must be driven with AC, not DC

- A steady voltage of only a few tens of millivolts leads to electrolysis of the liquid crystal, which eventually destroys the display

- Approach: The two electrodes of a segment are therefore driven with square waves in antiphase to produce an alternating voltage with zero mean

- The frequency is low, typically around 100 Hz, but must not be close to multiples of the AC mains (line) frequency (50 or 60 Hz)

- The output of many lights fluctuates at twice the frequency of the mains and the LCD appears to flicker if it is updated at a similar rate

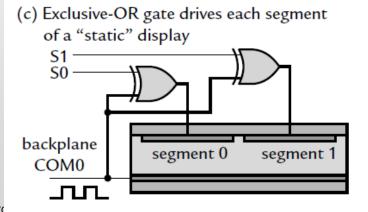

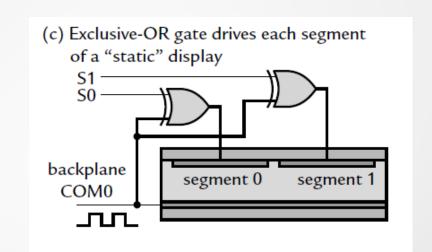

#### **Driving Multiple Segments in LCDs**

- Common backplane: COM A square wave provides a clock to bias the display

- Each segment on the front has a separate connection: S0, S1

- An exclusive-OR gate with a control signal to each segment:

- Si=0 => XOR gate transmits clock on COM0 unchanged => there is no potential difference between the electrodes, and the segment remains clear

- Si=1 => XOR inverts the clock so that an alternating bias is applied to the segment, which turns dark

- XOR gates could be real devices but it is straightforward to implement this inside the MCU by toggling the outputs periodically

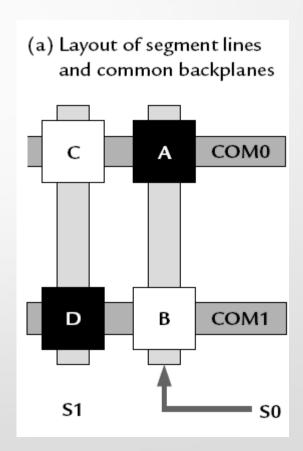

## Driving Multiple Segments in LCDs (cont'd)

- Static approach:

- One pin for each segment on display + one pin for backplane

- Problem: Large number of pins

#### Solution:

- Multiplexed displays require fewer pins (multiple segments share a single pin)

- Drawback: more trickier to multiplex LCDs because of the requirement for AC drive

- Example

- 4 segments (A, B, C, and D)

- 1 backplane

- Static: 5 pins

- Multiplexed: 4 pins

- 2 common backplanes (COM0, COM1)

- 2 signals (S0, S1)

- Segment A:  $V_{COM0} V_{S0}$ ; Segment B:  $V_{COM1} V_{S0}$

- Segment C: V<sub>COM0</sub> –V<sub>S1</sub>; Segment D: V<sub>COM1</sub> V<sub>S1</sub>

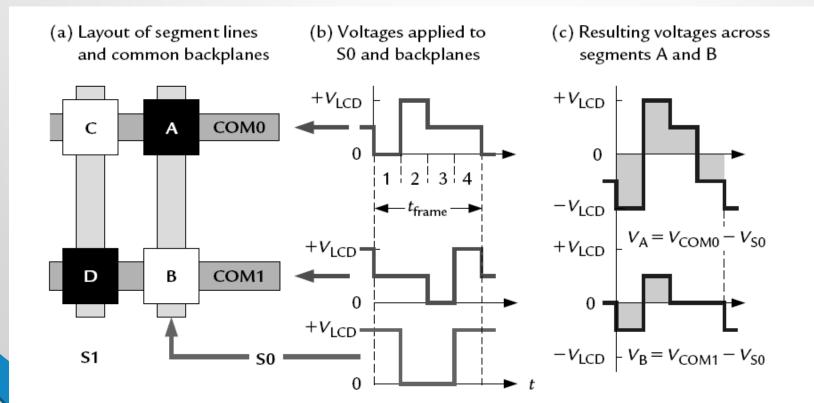

- Each period of the waveforms, called a frame, is divided into four phases:

- 1. The segments on COMO are addressed in the first phase by pulling COMO to ground (0 V).

- Segment A should be on and SO is therefore driven to its maximum value, V<sub>LCD</sub>

- $V_A = V_{COMO} V_{SO} = -V_{LCD}$

- The segments on COM1 should be inactive during this phase and it is therefore put at a "neutral" voltage of  $1/2V_{ICD}$

- $V_B = V_{COM1} V_{S0} = -1/2V_{ICD}$

- 2. The voltages in the second phase are the opposite of those in the first to ensure a pure AC signal with zero mean

- $V_{COM0} = V_{LCD}$  and  $V_{S0} = 0$  to give  $V_A = +V_{LCD}$

- The backplane that is not being addressed, COM1, remains at its neutral voltage of  $1/2V_{LCD}$  so that  $V_B = +1/2V_{LCD}$

- 3. Now it is the turn of COM1 to be addressed so it is pulled to ground and COM0 is set to neutral  $1/2V_{\rm LCD}$

- Segment B should be off and SO is therefore pulled to ground as well

- 4. This is the opposite of phase 3 to ensure that the mean voltage remains 0.

- It is not possible to apply either the maximum voltage  $\pm V_{LCD}$  at all times to segments that should be on nor a constant value of 0 to those that should be off

- Response of a segment depends on the root mean square (rms)

value of the bias across it

- Suppose that  $V_{LCD} = 3.0 \text{ V.}$  Then the values here are

- $Vrms\ A = \sqrt{5/8}\ V_{LCD} \approx 2.4V$

- Vrms  $B = \sqrt{1/8} V_{LCD} \approx 1.1 V$

- The rms voltages have a ratio of V5 and are sufficiently large and small to make the segments dark and clear, respectively

- The drive is no longer purely "digital" because a voltage of 1/2  $V_{LCD}$  is needed

## LCD\_A Display Clock

- Refresh rate: 30 Hz or faster to avoid flicker

- Higher frequencies give a clearer display but consume more current

- 2-way multiplexed: 2x2, 4 clocks per frame

- 4-way multiplexed display needs eight clock cycles per frame (4x2)

- fLCD must be at least 240 Hz

- ACLK is at the usual 32 KHz =>

32 K/240 = 136 or less,

so a factor of 128 would probably be chosen

#### LCD\_A Bias Voltage

- LCD\_A has an internal chain of resistors

- No external components are needed other than the display itself

- An external resistor chain can be used to reduce the current required. A variable resistor can be attached as a contrast control

#### LCD\_A Bias Voltage

- LCD\_A offers three choices for the voltage to drive the display:

- 1) Internal AVCC

- 2) An external voltage, which may be used with either the internal or an external divider

- 3) An internal charge pump, which provides an adjustable, regulated output in the range 2.60–3.44V, which can be controlled from software

- A reservoir capacitor CLCD of at least 4.7F for the charge pump must be connected to the LCDCAP pin

- Note: CPU may operate on low voltages

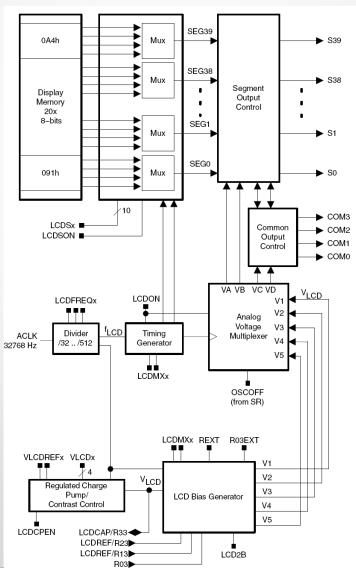

#### LCD\_A Controller

- Liquid Crystal Display (LCD) controller

- Included in several devices of the MSP430 families ('3xx and '4xx)

- Allows a rapid and simple way to interface with the program

- LCD controller commands the LCD panels generating voltage signals to the segments

- Features

- Display memory

- Automatic signal generation

- Configurable frame frequency

- Blinking capability

- Support for 4 types of LCDs:

- Static

- 2-mux, 1/2 bias

- 3-mux, 1/3 bias

- 4-mux, 1/3 bias

## LCD\_A Controller Block Diagram

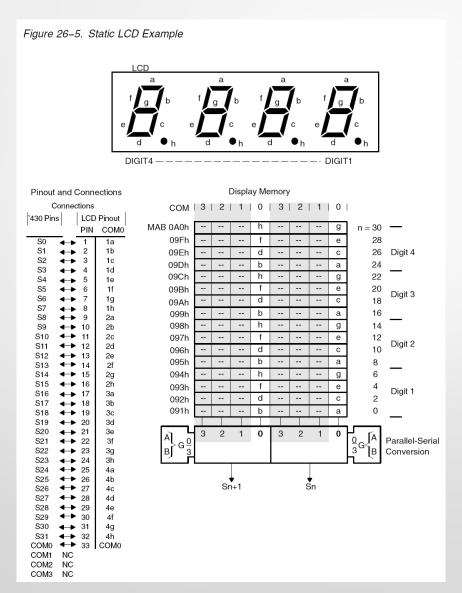

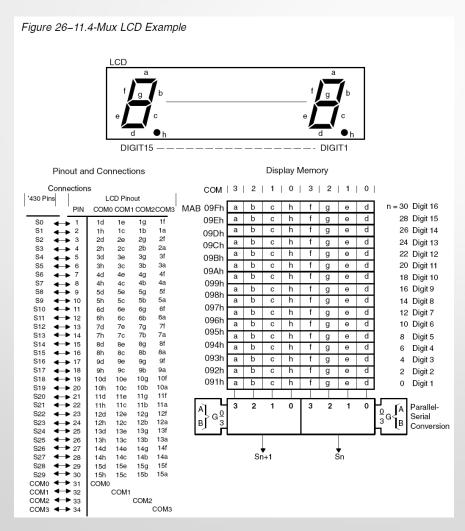

#### **LCD Memory Map**

- Each memory bit corresponds to one LCD segment, or is not used, depending on the mode

- To turn on an LCD segment, its corresponding memory bit is set

| Associated<br>Common Pins | 3 | 2 | 1 | 0 | 3 | 2             | 1 | 0 | A    | ssociated   |

|---------------------------|---|---|---|---|---|---------------|---|---|------|-------------|

| Address                   | 7 |   |   |   |   |               |   | 0 | n Se | egment Pins |

| 0A4h                      |   |   |   |   |   |               |   |   | 38   | 39, 38      |

| 0A3h                      | 1 | - |   |   | - |               |   |   | 36   | 37, 36      |

| 0A2h                      | - |   |   |   | - |               |   |   | 34   | 35, 34      |

| 0A1h                      | - |   |   |   |   |               |   |   | 32   | 33, 32      |

| 0A0h                      |   | - |   |   | - |               |   |   | 30   | 31, 30      |

| 09Fh                      |   |   |   |   |   |               |   |   | 28   | 29, 28      |

| 09Eh                      | - | - |   |   | 1 |               |   |   | 26   | 27, 26      |

| 09Dh                      | - |   |   |   | - |               |   |   | 24   | 25, 24      |

| 09Ch                      | - | 1 |   | - | i |               |   |   | 22   | 23, 22      |

| 09Bh                      | - | - |   |   | - |               |   |   | 20   | 21, 20      |

| 09Ah                      |   | 1 |   |   | 1 |               |   |   | 18   | 19, 18      |

| 099h                      | 1 | - |   |   | - |               |   |   | 16   | 17, 16      |

| 098h                      |   | - |   |   | - |               |   |   | 14   | 15, 14      |

| 097h                      | - | - |   |   | - |               |   |   | 12   | 13, 12      |

| 096h                      | - | - |   |   | - |               |   |   | 10   | 11, 10      |

| 095h                      |   | - |   |   | - |               |   |   | 8    | 9, 8        |

| 094h                      | - | - |   |   | 1 |               |   |   | 6    | 7, 6        |

| 093h                      |   |   |   |   |   |               |   |   | 4    | 5, 4        |

| 092h                      |   |   |   |   |   |               |   |   | 2    | 3, 2        |

| 091h                      | - |   |   |   |   |               |   |   | 0    | 1, 0        |

|                           | \ |   |   |   |   | $\overline{}$ |   |   |      |             |

| Sn+1 Sn                   |   |   |   |   |   |               |   |   |      |             |

#### **LCD Controller Operation**

- LCD controller supports blinking

- The LCDSON bit is ANDed with each segment's memory bit.

- When LCDSON = 1, each segment is on or off according to its bit value

- When LCDSON = 0, each LCD segment is off

- Timing generation

- Uses the f<sub>LCD</sub> signal to generate the timing for common and segment lines

- Proper frequency f<sub>LCD</sub> depends on the LCD's requirement for framing frequency and LCD multiplex rate

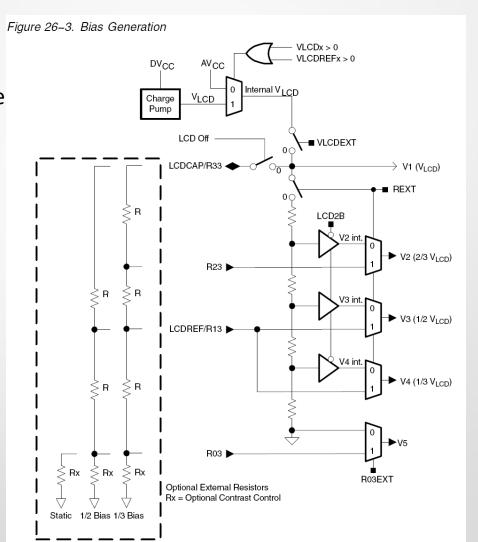

#### LCD\_A Voltage Generation

- Allows selectable sources for the peak output waveform voltage, V1, as well as the fractional LCD biasing voltages V2 – V5

- VLCD may be sourced from AVCC, an internal charge pump, or externally

- All internal voltage generation is disabled if the oscillator sourcing ACLK is turned off (OSCOFF = 1) or the LCD\_A module is disabled (LCDON = 0)

#### LCD\_A Voltage Selection

- Sourced from

- AVCC when VLCDEXT = 0, VLCDx = 0, and VREFx = 0.

- the internal charge pump when VLCDEXT = 0, VLCDPEN = 1, and VLCDx > 0

- The charge pump is always sourced from DVCC

- The VLCDx bits provide a software selectable LCD voltage from 2.6 V to 3.44 V (typical) independent of DVCC

- The internal charge pump may use an external reference voltage when VLCDREFx = 01. In this case, the charge pump voltage will be 3x the voltage applied externally to the LCDREF pin and the VLCDx bits are ignored.

- When VLCDEXT = 1, VLCD is sourced externally from the LCDCAP pin and the internal charge pump is disabled.

#### **Bias Generation**

- The fractional LCD biasing voltages, V2 – V5 can be generate internally or externally, independent of the source for VLCD

- REXT bit

#### LCD\_A Voltage Generation

- The contrast ratio depends on the used LCD display and the selected biasing scheme

- Table 26–1 shows the biasing configurations that apply to the different modes together with the RMS voltages for the segments turned on (VRMS,ON) and turned off (VRMS,OFF) as functions of VLCD. It also shows the resulting contrast ratios between the on and off states

Table 26-1.LCD Voltage and Biasing Characteristics

| Mode   | Bias<br>Config | LCDMx | LCD2B | COM<br>Lines | Voltage<br>Levels | V <sub>RMS,OFF</sub> /<br>V <sub>LCD</sub> | V <sub>RMS,ON</sub> /<br>V <sub>LCD</sub> | Contrast<br>Ratio<br>V <sub>RMS,ON</sub> /<br>V <sub>RMS,OFF</sub> |

|--------|----------------|-------|-------|--------------|-------------------|--------------------------------------------|-------------------------------------------|--------------------------------------------------------------------|

| Static | Static         | 00    | Χ     | 1            | V1, V5            | 0                                          | 1                                         | 1/0                                                                |

| 2-mux  | 1/2            | 01    | 1     | 2            | V1, V3, V5        | 0.354                                      | 0.791                                     | 2.236                                                              |

| 2-mux  | 1/3            | 01    | 0     | 2            | V1, V2, V4, V5    | 0.333                                      | 0.745                                     | 2.236                                                              |

| 3-mux  | 1/2            | 10    | 1     | 3            | V1, V3, V5        | 0.408                                      | 0.707                                     | 1.732                                                              |

| 3-mux  | 1/3            | 10    | 0     | 3            | V1, V2, V4, V5    | 0.333                                      | 0.638                                     | 1.915                                                              |

| 4-mux  | 1/2            | 11    | 1     | 4            | V1, V3, V5        | 0.433                                      | 0.661                                     | 1.528                                                              |

| 4–mux  | 1/3            | 11    | 0     | 4            | V1, V2, V4, V5    | 0.333                                      | 0.577                                     | 1.732                                                              |

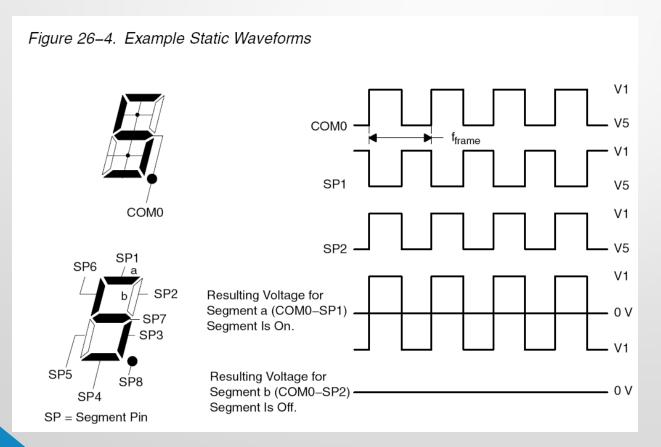

#### **Static Mode**

- Each MSP430 segment pin drives one LCD segment

- One common line, COM0, is used

#### **Static LCD Example**

## **Static Mode Software Example**

```

All eight segments of a digit are often located in four

display memory bytes with the static display method.

EQU

001h

а

b

EOU

010h

d

b

g

C

a

C

EQU

002h

EQU

020h

EOU

004h

EOU

040h

EQU

008h

EQU

080h

The register content of Rx should be displayed.

The Table represents the 'on'-segments according to the

content of Rx.

MOV.B Table (Rx),RY

; Load segment information

; into temporary memory.

(Ry) = 0000 0000 \text{ hfd}b \text{ geca}

MOV.B Ry, &LCDn

; Note:

; All bits of an LCD memory

d

b

g

e

C

a

' byte are written

; (Ry) = 0000 0000 0hfd bgec

RRA

Ry

MOV.B Ry, &LCDn+1

; Note:

b

g

; All bits of an LCD memory

; byte are written

RRA

Rv

(Ry) = 0000 0000 00hf dbge

MOV.B Ry, &LCDn+2

; Note:

b

h

d

g

; All bits of an LCD memory

' byte are written

; (Ry) = 0000 0000 000h fdbq

RRA

Ry

MOV.B Ry, &LCDn+3

: Note:

d

b

0

0

0

h

; All bits of an LCD memory

' byte are written

Table DB

a+b+c+d+e+f

; displays "0"

```

b+c:

. . . . . . . . . . .

. . . . . . . . . . .

; displays "1"

## THE UNIVERSITY OF ALABAMA IN HUNTSVILLE

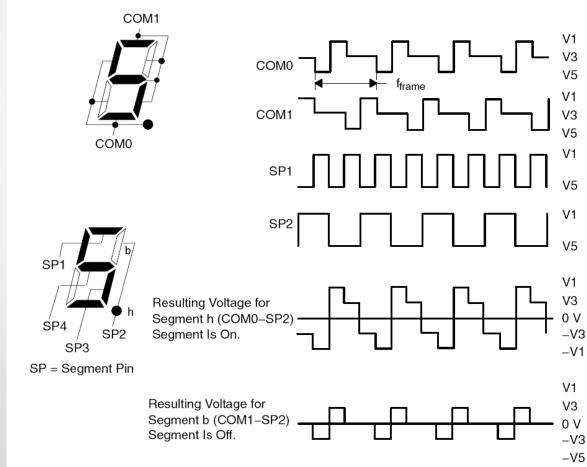

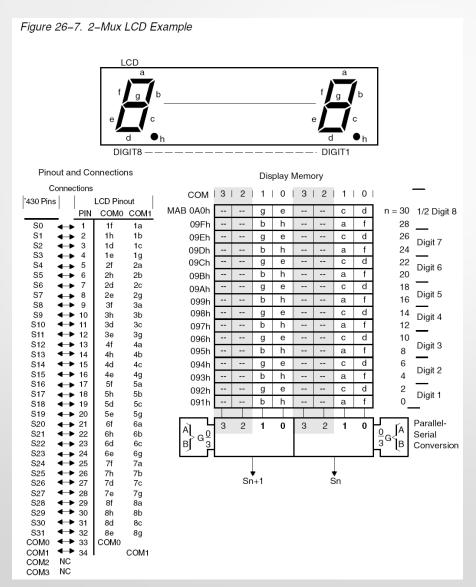

#### 2-MUX Mode

- Each MSP430 segment Figure 26–6. Example 2-Mux Waveforms

- pin drives two LCD segments

- Two common lines,

COM0 and COM1, are

used

- 2-mux example waverforms

$a = COM_1 - SP_1$

b=COM1-SP2

c=COM1-SP3

d=COMo-SP3

e=COMo-SP4

f=COMo-SP1

q = COM1 - SP4

#### 2-MUX LCD Example

#### 2-MUX Software Example

```

All eight segments of a digit are often located in two

display memory bytes with the 2mux display rate

EOU

002h

а

EQU

020h

EOU

008h

EQU

004h

EQU

040h

EQU

001h

EQU

080h

EQU

010h

The register content of Rx should be displayed.

The Table represents the 'on'-segments according to the

content of Rx.

. . . . . . . . . . .

MOV.B Table(Rx), Ry; Load segment information into

; temporary memory.

MOV.B Ry, &LCDn

; (Ry) = 0000 0000 \text{ gebh cdaf}

; Note:

; All bits of an LCD memory byte

; are written

RRA

Ry

; (Ry) = 0000 0000

0geb hcda

; (Ry) = 0000 0000 00ge bhcd

RRA

Ry

MOV.B Ry, &LCDn+1

; Note:

; All bits of an LCD memory byte

; are written

; displays "0"

Table DB

a+b+c+d+e+f

a+b+c+d+e+f+q ; displays "8"

DB

```

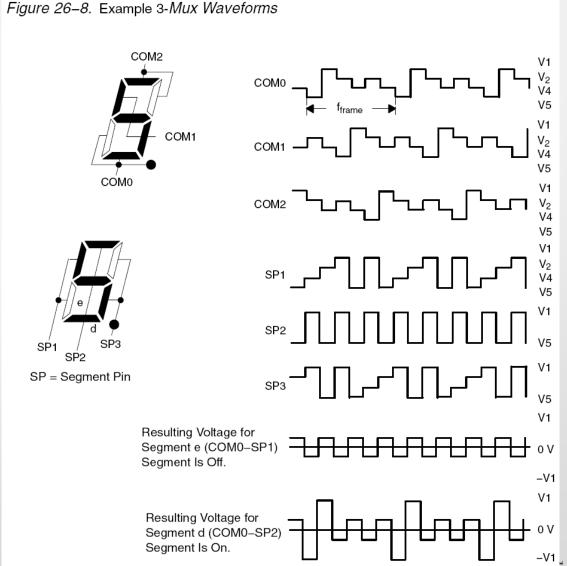

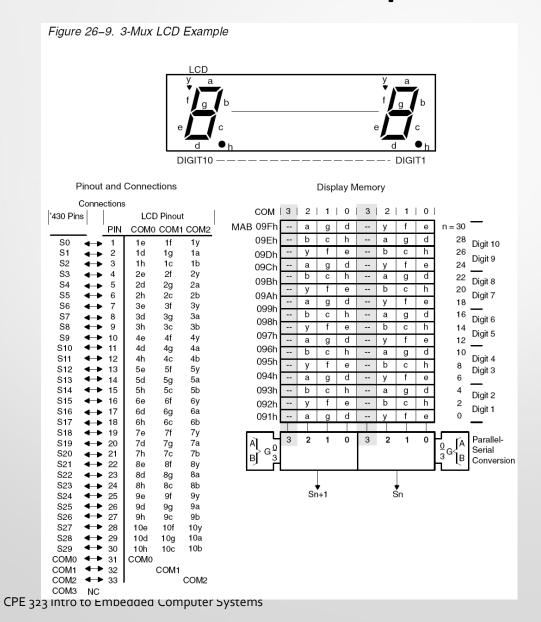

#### **3-MUX Mode Waverforms**

- Each MSP430 segment pin drives three LCD segments

- Three common lines,

COM0 and COM1, and

COM2 are used

- 3-mux example waverforms

#### 3-MUX LCD Example

#### **3-MUX Software Example**

```

The 3mux rate can support nine segments for each

digit. The nine segments of a digit are located in

1 1/2 display memory bytes.

EQU

0040h

0400h

0200h

EQU

0010h

0001h

EQU

0002h

0020h

EOU

0100h

EQU

0004h

The LSDigit of register Rx should be displayed.

The Table represents the 'on'-segments according to the

LSDigit of register of Rx.

The register Ry is used for temporary memory

ODDDIGRLA

; LCD in 3mux has 9 segments per

; digit; word table required for

; displayed characters.

Table (Rx), Ry; Load segment information to

; temporary mem.

; (Ry) = 0000 0bch 0agd 0yfe

MOV.B Ry, &LCDn

; write 'a, g, d, y, f, e' of

; Digit n (LowByte)

SWPB Ry

; (Ry) = 0agd 0yfe 0000 0bch

BIC.B #07h, &LCDn+1; write 'b, c, h' of Digit n

; (HighByte)

BIS.B Ry, &LCD<sub>n+1</sub>

EVNDIGRLA Rx

; LCD in 3mux has 9 segments per

; digit; word table required for

; displayed characters.

Table (Rx), Ry; Load segment information to

; temporary mem.

; (Ry) = 0000 0bch 0agd 0yfe

; (Ry) = 0000 bch0 agd0 vfe0

RLA Ry

; (Ry) = 000b ch0a gd0y fe00

RLA RV

; (Ry) = 00bc h0ag

d0yf e000

; (Ry) = 0bch 0agd 0yfe 0000

BIC.B #070h, &LCD_{n+1}

BIS.B Ry, &LCD<sub>n+1</sub>; write 'y, f, e' of Digit n+1

; (LowByte)

SWPB Rv

; (Ry) = 0yfe 0000 0bch 0agd

MOV.B Ry, &LCD<sub>n+2</sub>; write 'b, c, h, a, q, d' of

; Digit n+1 (HighByte)

Table DW

a+b+c+d+e+f ; displays "0"

; displays "1"

a+e+f+q

; displays "F"

```

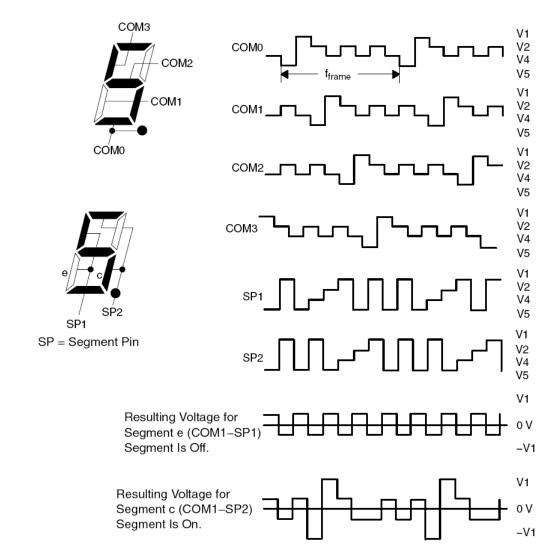

#### **4-MUX Mode Waverforms**

Figure 26-10. Example 4-Mux Waveforms

- Each MSP430 segment pin drives four LCD segments

- Four common lines, COM0, COM1, COM2, and COM3 are used

- 4-mux example waverforms

#### **4-MUX LCD Example**

#### **4-MUX Software Example**

```

The 4mux rate supports eight segments for each digit.

All eight segments of a digit can often be located in

one display memory byte

EQU

080h

EQU

040h

020h

EOU

001h

EQU

002h

EQU

EQU

008h

004h

EQU

EQU

010h

The LSDigit of register Rx should be displayed.

The Table represents the 'on'-segments according to the

content of Rx.

MOV.B Table(Rx), &LCDn; n = 1 \dots 15

; all eight segments are

; written to the display

; memory

a+b+c+d+e+f

; displays "0"

Table DB

; displays "1"

DB

b+c

b+c+d+e+g

; displays "d"

; displays "E"

DB a+d+e+f+g

a+e+f+g

; displays "F"

DB

```

## **LCD Control Registers**

Table 26-2.LCD Controller Registers

| Register                | Short Form | Register Type | Address | Initial State  |

|-------------------------|------------|---------------|---------|----------------|

| LCD_A control register  | LCDACTL    | Read/write    | 090h    | Reset with PUC |

| LCD memory 1            | LCDM1      | Read/write    | 091h    | Unchanged      |

| LCD memory 2            | LCDM2      | Read/write    | 092h    | Unchanged      |

| LCD memory 3            | LCDM3      | Read/write    | 093h    | Unchanged      |

| LCD memory 4            | LCDM4      | Read/write    | 094h    | Unchanged      |

| LCD memory 5            | LCDM5      | Read/write    | 095h    | Unchanged      |

| LCD memory 6            | LCDM6      | Read/write    | 096h    | Unchanged      |

| LCD memory 7            | LCDM7      | Read/write    | 097h    | Unchanged      |

| LCD memory 8            | LCDM8      | Read/write    | 098h    | Unchanged      |

| LCD memory 9            | LCDM9      | Read/write    | 099h    | Unchanged      |

| LCD memory 10           | LCDM10     | Read/write    | 09Ah    | Unchanged      |

| LCD memory 11           | LCDM11     | Read/write    | 09Bh    | Unchanged      |

| LCD memory 12           | LCDM12     | Read/write    | 09Ch    | Unchanged      |

| LCD memory 13           | LCDM13     | Read/write    | 09Dh    | Unchanged      |

| LCD memory 14           | LCDM14     | Read/write    | 09Eh    | Unchanged      |

| LCD memory 15           | LCDM15     | Read/write    | 09Fh    | Unchanged      |

| LCD memory 16           | LCDM16     | Read/write    | 0A0h    | Unchanged      |

| LCD memory 17           | LCDM17     | Read/write    | 0A1h    | Unchanged      |

| LCD memory 18           | LCDM18     | Read/write    | 0A2h    | Unchanged      |

| LCD memory 19           | LCDM19     | Read/write    | 0A3h    | Unchanged      |

| LCD memory 20           | LCDM20     | Read/write    | 0A4h    | Unchanged      |

| LCD_A port control 0    | LCDAPCTL0  | Read/write    | 0ACh    | Reset with PUC |

| LCD_A port control 1    | LCDAPCTL1  | Read/write    | 0ADh    | Reset with PUC |

| LCD_A voltage control 0 | LCDAVCTL0  | Read/write    | 0AEh    | Reset with PUC |

| LCD_A voltage control 1 | LCDAVCTL1  | Read/write    | 0AFh    | Reset with PUC |

## **LCD\_A Control Register**

#### LCDACTL, LCD\_A Control Register

| _ | 7    | 6 5      |      | 4      | 3    | 2      | 1      | 0     |

|---|------|----------|------|--------|------|--------|--------|-------|

|   |      | LCDFREQx |      | LCDMXx |      | LCDSON | Unused | LCDON |

| Ī | rw-0 | rw-0     | rw-0 | rw-0   | rw-0 | rw-0   | rw-0   | rw-0  |

| LCDFREQx | Bits<br>7-5 | LCD frequency select. These bits select the ACLK divider for the LCD frequency.  000 Divide by 32  001 Divide by 64  010 Divide by 96  011 Divide by 128  100 Divide by 192  101 Divide by 256  110 Divide by 384  111 Divide by 512                                             |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCDMXx   | Bits<br>4-3 | LCD mux rate. These bits select the LCD mode.  00 Static  01 2-mux  10 3-mux  11 4-mux                                                                                                                                                                                           |

| LCDSON   | Bit 2       | LCD segments on. This bit supports flashing LCD applications by turning off all segment lines, while leaving the LCD timing generator and R33 enabled.  O All LCD segments are off  All LCD segments are enabled and on or off according to their corresponding memory location. |

| Unused   | Bit 1       | Unused                                                                                                                                                                                                                                                                           |

| LCDON    | Bit 0       | LCD On. This bit turns on the LCD_A module.  CCD_A module off.  LCD_A module on.                                                                                                                                                                                                 |

## **LCD\_A Port Control Register**

| LCDAPCTL0, LCD_A Port Control Register 0                                                                      |        |                                                          |                                              |                                         |       |             |                    |  |  |

|---------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------|----------------------------------------------|-----------------------------------------|-------|-------------|--------------------|--|--|

| 7                                                                                                             | 6      | 5                                                        | 4                                            | 3                                       | 2     | 1           | 0                  |  |  |

| LCDS28                                                                                                        | LCDS24 | LCDS20                                                   | LCDS16                                       | LCDS12                                  | LCDS8 | LCDS4       | LCDS0 <sup>†</sup> |  |  |

| rw-0                                                                                                          | rw-0   | rw-0                                                     | rw-0                                         | rw-0                                    | rw-0  | rw-0        | rw-0               |  |  |

| † Segments S0–S3 on the MSP430FG461x devices are disabled from LCD functionality when charge pump is enabled. |        |                                                          |                                              |                                         |       |             |                    |  |  |

| LCDS28                                                                                                        | Т      |                                                          | ffects pins w<br>D function.                 | vith multiplex<br>port function         |       | . Dedicated | LCD pins           |  |  |

| LCDS24                                                                                                        | Т      | CD segment<br>his bit only a<br>re always LC<br>Multiple | 24 to 27 end<br>ffects pins w<br>D function. | able<br>vith multiplex<br>port functior |       | . Dedicated | LCD pins           |  |  |

| LCDS20                                                                                                        | Т      |                                                          | ffects pins w<br>D function.                 | vith multiplex<br>port function         |       | . Dedicated | LCD pins           |  |  |

| LCDS16                                                                                                        | Т      |                                                          | ffects pins w<br>D function.                 | vith multiplex<br>port function         |       | . Dedicated | LCD pins           |  |  |

| LCDS12                                                                                                        | Т      |                                                          | ffects pins w<br>D function.                 | ith multiplex<br>port function          |       | . Dedicated | LCD pins           |  |  |

| LCDS8                                                                                                         | Т      |                                                          | ffects pins w<br>D function.                 | vith multiplex<br>port function         |       | . Dedicated | LCD pins           |  |  |

| LCDS4                                                                                                         | Т      |                                                          | ffects pins w<br>D function.                 | ith multiplex<br>port function          |       | . Dedicated | LCD pins           |  |  |

| LCDS0                                                                                                         | Т      |                                                          | ffects pins w<br>D function.                 | vith multiplex<br>port function         |       | . Dedicated | LCD pins           |  |  |

## LCD\_A Port Control Register (1)

| LCDAPCTL1, LCD_A Port Control Register 1 |             |                                                                                                                                                                                              |      |      |      |        |        |  |  |  |

|------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|--------|--|--|--|

| 7                                        | 6           | 5                                                                                                                                                                                            | 4    | 3    | 2    | 1      | 0      |  |  |  |

|                                          |             | Unu                                                                                                                                                                                          | sed  |      |      | LCDS36 | LCDS32 |  |  |  |

| rw-0                                     | rw-0        | rw-0                                                                                                                                                                                         | rw-0 | rw-0 | rw-0 | rw-0   | rw-0   |  |  |  |

| Unused                                   | Bits<br>7–2 | Unused                                                                                                                                                                                       |      |      |      |        |        |  |  |  |

| LCDS36                                   | Bit 1       | LCD segment 36 to 39 enable This bit only affects pins with multiplexed functions. Dedicated LCD pins are always LCD function.  Multiplexed pins are port functions.  Pins are LCD functions |      |      |      |        |        |  |  |  |

| LCDS32                                   | Bit 0       | LCD segment 32 to 35 enable This bit only affects pins with multiplexed functions. Dedicated LCD pins are always LCD function.  Multiplexed pins are port functions.  Pins are LCD functions |      |      |      |        |        |  |  |  |

## LCD\_A Voltage Control Register (0)

| LCDAVCTL0, LCD_A Voltage Control Register 0 |                   |                                                                              |                                        |         |      |      |       |  |  |  |

|---------------------------------------------|-------------------|------------------------------------------------------------------------------|----------------------------------------|---------|------|------|-------|--|--|--|

| 7                                           | 6                 | 5                                                                            | 4                                      | 3       | 2    | 1    | 0     |  |  |  |

| Unused                                      | R03EXT            | REXT                                                                         | VLCDEXT                                | LCDCPEN | VLCD | REFx | LCD2B |  |  |  |

| rw-0                                        | rw-0              | rw-0                                                                         | rw-0                                   | rw-0    | rw-0 | rw–0 | rw-0  |  |  |  |

| Unused<br>R03EXT                            |                   |                                                                              |                                        |         |      |      |       |  |  |  |

| HUSEAT                                      |                   | 1 1 1 1 1 00                                                                 |                                        |         |      |      |       |  |  |  |

| REXT                                        |                   | generale a montany                                                           |                                        |         |      |      |       |  |  |  |

| VLCDEXT                                     | Bit 4 V<br>0<br>1 |                                                                              | select<br>generated in<br>sourced exte |         |      |      |       |  |  |  |

| LCDCPEN                                     | Bit 3 C<br>0<br>1 | Charge pump enable.  Charge pump disabled.                                   |                                        |         |      |      |       |  |  |  |

| VLCDREFx                                    | 2-1 00            | Charge pump reference select 00 Internal 01 External 10 Reserved 11 Reserved |                                        |         |      |      |       |  |  |  |

| LCD2B                                       | Bit 0 B<br>0<br>1 | Bias select. LCD2B is ignored when LCDMx = 00. 0 1/3 bias                    |                                        |         |      |      |       |  |  |  |

## LCD\_A Voltage Control Register (1)

| 7      | 6           | 5                                                                                                                                                                               | 4                                                                 | 3                       | 2    | 1    | 0    |  |  |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|------|------|------|--|--|

|        | Unused      | I                                                                                                                                                                               |                                                                   | VLCDx                   |      |      |      |  |  |

| rw-0   | rw-0        | rw-0                                                                                                                                                                            | rw-0                                                              | rw-0                    | rw-0 | rw-0 | rw-0 |  |  |

| Unused | Bits<br>7–5 | Unused                                                                                                                                                                          |                                                                   |                         |      |      |      |  |  |

| VLCDx  | Bits<br>4–1 | Charge pump<br>be enabled. A<br>and VLCDEX<br>0000 Charge p<br>0001 V <sub>LCD</sub> = 2<br>0010 V <sub>LCD</sub> = 2<br>0110 V <sub>LCD</sub> = 2<br>0101 V <sub>LCD</sub> = 2 | $V_{CC}$ is used $\Gamma = 0$ . pump disable 2.60 V 2.72 V 2.78 V | for V <sub>LCD</sub> wh |      |      |      |  |  |

Unused

Bit 0

Unused

$V_{LCD} = 2.90 \text{ V}$  $V_{LCD} = 2.96 \text{ V}$  $V_{LCD} = 3.02 \text{ V}$  $V_{LCD} = 3.08 \text{ V}$  $V_{LCD} = 3.14 \text{ V}$  $V_{LCD} = 3.20 \text{ V}$  $V_{LCD} = 3.26 \text{ V}$  $V_{LCD} = 3.32 \text{ V}$  $V_{LCD} = 3.38 \text{ V}$  $V_{LCD} = 3.44 \text{ V}$

LCDAVCTL1, LCD\_A Voltage Control Register 1

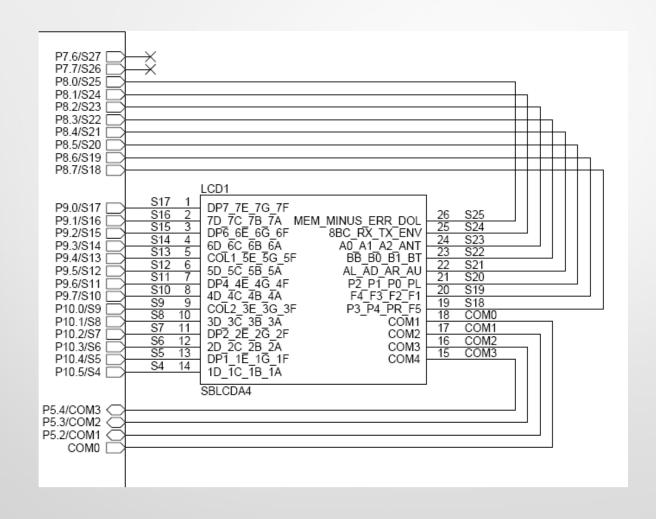

#### **DRFG4618 LCD Interface**

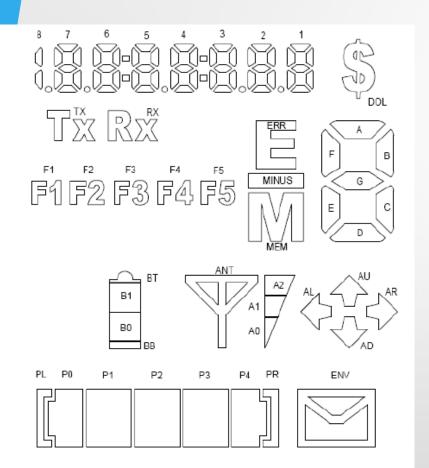

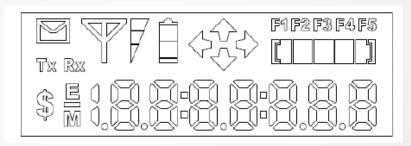

## Softbaugh LCD SBLCDA4: Segment Description

SBLCDA<sub>4</sub> Display

## Mapping SBCDA4 segments to MSP430 pites in HUNTSVILLE (TI Experimenter board)

| l' I              | COM:          |      |     | 2              | 1   | 0   | 3   | 2  | 1  | 0   | LCD        | MCD420        |

|-------------------|---------------|------|-----|----------------|-----|-----|-----|----|----|-----|------------|---------------|

| display<br>memory | MSP430<br>pin | pin  |     | S <sub>n</sub> | + 1 |     |     | S  | n  |     | LCD<br>pin | MSP430<br>pin |

| LCDM13            | S25           | •    | МЕМ | MIN            | ERR | DOL | 8BC | RX | TX | ENV | P25        | S24           |

| LCDM12            | S23           | P24  | A0  | A1             | A2  | ANT | ВВ  | ВО | B1 | ВТ  | P23        | S22           |

| :                 | :             | :    |     |                |     |     |     |    |    |     | :          | :             |

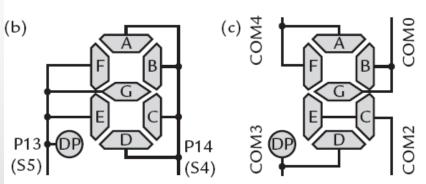

| LCDM4             | S7            | P11  | DP2 | 2E             | 2G  | 2F  | 2D  | 2C | 2B | 2A  | P12        | S6            |

| LCDM3             | S5            | P13  | DP1 | 1E             | 1G  | 1F  | 1D  | 1C | 1B | 1A  | P14        | S4            |

|                   |               | Bit: | 7   | 6              | 5   | 4   | 3   | 2  | 1  | 0   |            |               |